# How 3D NAND Stacks Up

Report No. FI-NFL-3DM-0114

© 2014 Forward Insights. All Rights Reserved. Reproduction and distribution of this publication in any form in whole or in part without prior written permission is prohibited. The information contained herein has been obtained from sources believed to be reliable. Forward Insights does not guarantee the accuracy, validity, completeness or adequacy of such information. Forward Insights will not be liable for any damages or injuries arising from the use of such information including, without limitation, errors, omissions or inadequacies in the information contained herein or for the interpretation thereof. The opinions expressed herein are subject to change without notice.

#### **Contents**

| ContentsIII                                                                                   |    |

|-----------------------------------------------------------------------------------------------|----|

| LIST OF FIGURES                                                                               |    |

| LIST OF TABLESXII                                                                             |    |

| EXECUTIVE SUMMARY                                                                             |    |

| NAND FLASH MEMORY                                                                             |    |

| NAND Flash Memory Technology Evolution                                                        | 4  |

| Floating Gate Memory Cell Scaling Challenges                                                  | 7  |

| Program Voltages and WL-WL Dielectric Breakdown                                               | 7  |

| Number of Floating Gate Electrons, Charge Cross-talk, and Random Telegraph Noise              | 9  |

| IPD Scaling of Electrical Thickness and Program Saturation: Can a Planar Cell be a Solution?. | 10 |

| NAND alternative: Charge Trapping Memory Cell                                                 | 13 |

| BD NAND ALTERNATIVES                                                                          |    |

| Conventional Approach                                                                         | 20 |

| Samsung Stacking by Single Crystal Deposition                                                 | 20 |

| Concept                                                                                       | 21 |

| Advantages and Disadvantages                                                                  | 25 |

| Challenges                                                                                    | 26 |

| Nonconventional approach                                                                      | 30 |

| Horizontal channel – horizontal gate                                                          | 30 |

| Concept                                                                                       | 30 |

| Advantages/Disadvantages                                                                      | 33 |

| Challenges                                                                                    | 35 |

| Vertical gate - Macronix TFT – Samsung VG-NAND                                                | 36 |

| Concept                                                                                       | 36 |

| Advantages/Disadvantages                                                                      | 44 |

| Challenges                                                                                    | 46 |

| Vertical Channel - Punch Structure                                                            | 47 |

| Toshiba BiCS                                                                                  | 47 |

| Concept - 1st Generation                                                                      | 47 |

| Advantages and Disadvantages                                                                  | 51 |

| Concept - $2^{nd}$ Generation $\rightarrow$ p-BiCS structure                                  | 55 |

| Challenges                                                                                    | 65 |

| Sa  | amsung TCAT                                     | 66   |

|-----|-------------------------------------------------|------|

|     | Concept                                         | 66   |

|     | Advantages                                      | 70   |

|     | Disadvantages                                   | 70   |

|     | Challenges                                      | .70  |

| Hy  | nix Vertical Cylindrical Floating-gate          | 71   |

|     | Concept                                         | 71   |

|     | Advantages                                      | 76   |

|     | Disadvantages                                   | .76  |

|     | Challenges                                      | 76   |

| Sł  | K Hynix SMArT – Stacked Memory Array Transistor | . 77 |

|     | Concept                                         | . 77 |

|     | Advantages                                      | . 79 |

|     | Disadvantages                                   | 79   |

|     | Challenges                                      | . 79 |

| Ve  | ertical Channel - Channel Wrap-around Structure | . 80 |

| Sa  | amsung VSAT – Vertical Stacked Array Transistor | 80   |

|     | Concept                                         | 80   |

|     | Advantages                                      | 84   |

|     | Disadvantages                                   | 84   |

|     | Challenges                                      | 85   |

| Сом | PARISON OF 3D MEMORY CONCEPTS                   |      |

|     | Cell Size                                       |      |

|     | Disturbs                                        | 90   |

|     | Cell Efficiency                                 |      |

|     | Number of Bits per cell Capability              |      |

|     | Yield                                           |      |

|     | Performance                                     |      |

|     | Endurance                                       |      |

|     | Retention                                       |      |

|     | Power Consumption                               | L01  |

|     | Stackability2                                   | L02  |

| Summary                |      | 105 |

|------------------------|------|-----|

| Outlook                | .108 |     |

| 3D NAND Status         |      | 109 |

| Intel/Micron           |      | 109 |

| Macronix               |      | 110 |

| Samsung                |      | 110 |

| SanDisk/Toshiba        |      | 111 |

| SK Hynix               |      | 112 |

| 3D NAND Roadmap        |      | 114 |

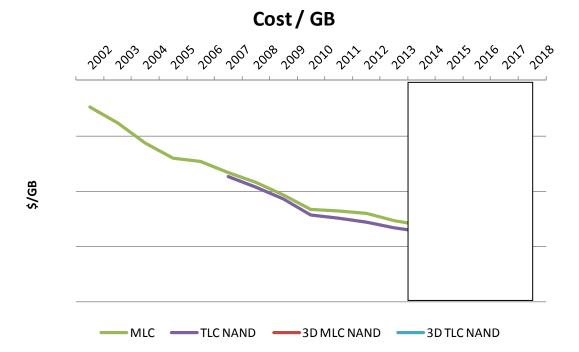

| 3D NAND Cost Trend     |      | 115 |

| References             | .117 |     |

| ABOUT THE AUTHORS      | .123 |     |

| ABOUT NAMLAB           | .125 |     |

| Contact                |      | 126 |

| ABOUT FORWARD INSIGHTS | .127 |     |

| Services               |      | 127 |

| Contact                |      | 127 |

## **List of Figures**

| Figure 1.   | NAND Flash Technology Evolution                                                         | 5                |

|-------------|-----------------------------------------------------------------------------------------|------------------|

| -           | NAND Flash Memory Coupling Ratio, other coupling components, and Cross-talk             |                  |

|             | hInsights/Forward Insights]                                                             | 6                |

| Figure 3.   | Bit line pitch scaling limitation issue [Forward Insights]                              | 7                |

| Figure 4.   | NAND Flash Cells with Metal Control Gate comprising (a) a thick TiN and (b) a 5nm       |                  |

|             | 1]                                                                                      | 8                |

| Figure 5.   | 25 nm Intel/Micron NAND Flash Technology [3]                                            | 8                |

|             | Electrons Stored on the Floating Gate [4]                                               |                  |

|             | Simulated Random Telegraph Noise Amplitude Distributions for scaled Floating Gate       |                  |

|             | y Nodes [5]                                                                             | 10               |

| Figure 8.   | Gate Coupling Ratio Variation by Different Poly Plug Depth and Program Saturation       |                  |

|             | , , , , , , , , , , , , , , , , , , ,                                                   | 11               |

|             | Program and Erase Behavior of Fully Planar FG Capacitors and Field Conditions for       |                  |

|             | G Options [6]                                                                           | 12               |

|             |                                                                                         | 13               |

| Figure 11.  | Tunneling current characteristic for direct tunnelling with different oxide thicknesses |                  |

|             |                                                                                         | 14               |

|             | Erase characteristics of a charge trap memory device with various metal gates offering  |                  |

|             | ons comparable to n+-poly until p+-poly silicon as well as values in-between [8]        | 14               |

|             | Tradeoff between retention and erase performance for charge trap stacks with different  |                  |

|             | try of the SiN charge storage layer [9]                                                 |                  |

|             | Cross sectional view through the gate all-around structure used in the comparison of    |                  |

| •           | al performance of SONOS stacks in planar and this structure [10]                        | 16               |

|             | Illustration of the improvement in the field distribution of the SONOS structure by the | 10               |

| -           | oupling due to the gate all-around arrangement [9]                                      | 16               |

|             | Comparison of the program and erase performance of a planar SONOS stack memory          | 10               |

| •           | with a gate all-around structure taking advantage of the improved coupling ratio [9]    | 17               |

|             | Comparison of the retention loss for planar and surrounding gate SONOS structures       | • ′              |

|             | Comparison of the retention ross for plantar and surrounding gate Serves structures     | 17               |

|             | Performance improvement of program and erase due to the scaling of the Si-pillar        | 1,               |

|             | hancing the gate coupling of the charge trap layer [11]                                 | 18               |

|             | Image of the test chip with stacked NAND floating gate structure in the 45nm node       | 10               |

| •           |                                                                                         | 20               |

|             | Estimation of NAND fabrication costs as the bit density increases for conventional      | 20               |

| •           | · · · · · · · · · · · · · · · · · · ·                                                   | 21               |

|             | Schematic cross section of the 3-D TANOS NAND showing a first arrangement of            | <b>4</b> 1       |

|             | on Si substrate level and a second level of NAND memory cell strings stacked above      |                  |

|             | on 51 substrate level and a second level of tVAIVD memory cen strings stacked above     | 21               |

|             | SEMs of 3D stacked NAND cell string. The 2nd active layer is SOI-like perfect           | <b>4</b> 1       |

|             | tal [12]                                                                                | วว               |

| Figure 23.  | Layout and vertical structure of word-lines and x-decoders for the doubly stacked       | <i></i>          |

| •           |                                                                                         | วว               |

| Figure 24.  | Sh memory cell array. [12]                                                              | ∠∠<br><b>?</b> 2 |

| 1 1guit 24. | Key process steps of 3D INAIND Highlory. [12]                                           | ۷3               |

| Figure 25. Comparison of erase operation (a) well bias initiated erase by block, (b) erase by page           |

|--------------------------------------------------------------------------------------------------------------|

| without well bias in the floating body case [12]23                                                           |

| Figure 26. (a) TEM cross section image of LEG Si film; Inset image shows sub-grain boundary in               |

| protrusion. (b) Modelling of LEG process; selective melting of a-Si film and solidification from             |

| seed. [15]                                                                                                   |

| Figure 27. Process scheme with amorphous layer formation on seeds to initiate laser epitaxial                |

| growth of single crystal Si film resulting in stacked transistor bodies for 3D memories. [16]24              |

| Figure 28. Tilted SEM image with protrusions which are precisely located in the center between               |

| neighbouring seeds. [15]                                                                                     |

| Figure 29. Schematic illustration of thermal budget impact on device structure: S/D junctions                |

| between NAND wordlines diffuse below gate contacts and cause punch-through device failure. [16]28            |

| Figure 30. Simulated temperature profiles for various laser pulse durations. The penetration                 |

| depths can be controlled by the pulse durations [17]                                                         |

| Figure 31. The basic concept of the DG-TFT-SONOS Flash showing simultaneous shielding of                     |

| stored charge during pass voltage application and intimate electrical interaction for good short             |

| channel control. [18]                                                                                        |

| Figure 33. SIMS analysis of antimony-implanted LPCVD amorphous silicon, showing negligible                   |

| diffusion [18]                                                                                               |

| Figure 34. Sheet resistance of antimony implanted into LPCVD amorphous silicon and annealed.                 |

| [18]                                                                                                         |

| Figure 35. Cycling endurance of the mid-cell of a 32 cell string of minimum feature sized devices.           |

| No other second-gated memory devices are used in the cycling [18]                                            |

| Figure 36. Retention after cycling 10 <sup>5</sup> cycles showing good performance after extrapolation to 10 |

| years. [18]                                                                                                  |

| Figure 37. Tri-gate structure of the TFT device based SONOS memory cell [19]34                               |

| Figure 38. TEM cross sections of TFT NAND strings perpendicular to the wordline and along the                |

| wordline direction [19]                                                                                      |

| Figure 39 Schematic view on single node of the vertical gate structure with two memory elements              |

| on the left and right of the horizontal channel [21]                                                         |

| Figure 40 Principle of integrated structure of the 3D vertical gate approach presented by                    |

| Macronix. The strings are addressed by the selector devices on the right end of the NAND string              |

| [22]36                                                                                                       |

| Figure 41 Fabrication process of the vertical gate structure presented by Samsung shown for one              |

| channel stack [23]                                                                                           |

| Figure 42. Cross sectional view through the stacked bitlines with the vertical gates aside [22],             |

| [23]                                                                                                         |

| Figure 43. Comparison of the vertical gate NAND structures proposed by Macronix (left) and                   |

| Samsung (right) by a top down view on one plane [NaMLab]                                                     |

| Figure 44. Implant scheme for the select transistors to distinguish between the stacked planes               |

| connected to the same bitline [23]                                                                           |

| Figure 45. Calculation of the additional area needed for the string select devices to address the            |

| different planes relative to the cell area [NaMLab]                                                          |

| Figure 46. Schematic diagram of the Twisted BL (Split-page) VG architecture, featuring                       |

| staircase BL contacts [24]                                                                                   |

| Figure 47. a) MiLC concept to form staircase BL-contacts, using binary sum of a few etching                  |

| steps and b) cross-sectional view through the etched staircase BL-contacts [24]40                            |

| Figure 48. Principle of dual-channel NAND Flash [25]                                                         |

| Figure 49. Dual-channel 3D-NAND concept [25]                                                                 |

| Figure 50. a) programming method in the dual-channel 3D-NAND and b) corresponding array                                         |

|---------------------------------------------------------------------------------------------------------------------------------|

| equivalent circuit; Cell A is the programmed cell                                                                               |

| Figure 51. Comparison of program and erase behavior for conventional n-channel NAND vs.                                         |

| proposed dual-channel NAND [25]                                                                                                 |

| Figure 52. Samsung electrical data a) endurance with 2.5V window and b) retention at room                                       |

| temperature [23]                                                                                                                |

| Figure 53. Macronix electrical data a) endurance of 4 different devices and b) retention before and                             |

| after cycling [22]                                                                                                              |

|                                                                                                                                 |

| trap concept [26]                                                                                                               |

| Figure 55 Samsung vertical stacking of 4 blocks consisting of vertical gate NAND arrays [23]45                                  |

| Figure 56. Equivalent circuit of the BiCS arrangement of vertical NAND strings. [27]47                                          |

| Figure 57. Birds-eye view of BiCS flash memory. N <sub>CG</sub> is the number of control gates. N <sub>SG</sub> is the          |

| number of rows of pillars sharing an upper select gate. [27]                                                                    |

| Figure 58. (a) Cross section of BiCS flash memory string, (b) Cross section of vertical SONOS                                   |

| cell [27]48                                                                                                                     |

| Figure 59. Stair-like structure at the edge of control gate plates and upper select gate pitch [27]49                           |

| Figure 60. Fabrication sequence of BiCS flash memory [27]                                                                       |

| Figure 61. Cross sectional SEM image and schematic illustration of the latest reported BiCS cell                                |

| array. [28]                                                                                                                     |

| Figure 62. I <sub>d</sub> -V <sub>g</sub> characteristics after program and erase operation of each of the different cells of   |

| a NAND string (non-optimized structure with respect to disturb). [28]                                                           |

| Figure 63. Schematic potential profile in unselected pillars during program operation. The                                      |

| potential of pillars boosted by $V_{pgm}$ is seen to be higher than $V_{pass}$ , resulting in a negative $V_{th}$ shift         |

| of the disturbed cells. [28]                                                                                                    |

| Figure 64. V <sub>th</sub> shift after program disturb of programmed cells in unselected pillars. A negative                    |

| $V_{th}$ shift is suppressed if suitable $V_{pass}$ is selected [28]                                                            |

| Figure 65. Improved concept of changing lower select gate plates to line and space pattern in                                   |

| order to boost unselected pillars by turning on/off USG and LSG synchronously. [28]54                                           |

| Figure 66. V <sub>th</sub> shift after read disturb on unselected pillars. V <sub>th</sub> shift is suppressed significantly by |

| changing the lower select gate plates into line and space patterns [25]                                                         |

| Figure 67. Structure of the pipe BiCS concept in a side view up to the contact level [29]55                                     |

| Figure 68. SEM picture of the select array in a pipe BiCS structure showing the connections to                                  |

| suorceline and bitline in detail [29]                                                                                           |

| Figure 69. Detailed view on the basic structure of the p-BiCS (a-left) and straight BiCS (a-right)                              |

| and the measurement of the respective doping profiles (b) [29]                                                                  |

| Figure 70. Process steps to fabricate the array of p-BiCS [29], [30]                                                            |

| Figure 71. Slit formation and wordline metallisation to improve dynamic performance in the                                      |

| BiCS concept [30]                                                                                                               |

| Figure 72. Sectional view through the macaroni structure proposed by Toshiba to reduce $V_T$                                    |

| distribution [31]                                                                                                               |

| Figure 73. Principle of the fabrication of the Si-pillar with dielectric filler to reduce the effect of                         |

| charge scattering [31]                                                                                                          |

| Figure 74. Improvement of the electrical characteristic of vertical channel devices by introducing                              |

| a dielectric filler inside the channel pillar; a) in the $V_T$ distribution width and b) in the sub-threshold                   |

| region [30]                                                                                                                     |

| Figure 75. Sideview at a BiCS structure demonstrating the contact scheme and arrangement of the                                 |

| structure and the fan-out areas [33]                                                                                            |

| L 1                                                                                                                             |

| Figure 76. Overv     | view of the BiCS test chip a) and the cross section through the control gate                         |

|----------------------|------------------------------------------------------------------------------------------------------|

| contact area b) [33  |                                                                                                      |

| Figure 77. Progra    | am/erase performance 1 <sup>st</sup> generation and 2 <sup>nd</sup> generation BiCS [29], [31]61     |

|                      | tion performance 1 <sup>st</sup> generation (a) and 2 <sup>nd</sup> generation (b) BiCS [28], [29]61 |

|                      | rance measurement results of 2 <sup>nd</sup> generation p-BiCS [29]                                  |

|                      | led investigation of the disturb immunity of P-BiCS (solid circle) and straight-                     |

|                      | ned circle) [34]63                                                                                   |

| Figure 81. Electr    | rical scheme to erase a p-BiCS string by GIDL generated holes in the select                          |

| transistor and trans | sfer the holes into the pipe [32]63                                                                  |

|                      | urement of the control gate resistance dependent on the silicide layer thickness                     |

|                      | ent in the pulse shape of the control gate [29]64                                                    |

|                      | am and erase characteristics of SONONS based BiCS cells [28]66                                       |

|                      | onal view through a single cell of the TCAT concept with vertical channel [30]66                     |

|                      | ration scheme of the TCAT concept [33]                                                               |

|                      | onal view and SEM picture through the vertical string of a TCAT array (a) cut                        |

|                      | ne and (b) cut perpendicular to source-/bitline [33]                                                 |

|                      | fer characteristic in a TCAT string with 6 memory cells (a) and V <sub>TH</sub> distribution         |

| (b) [33]             |                                                                                                      |

|                      | am/erase characteristics of TCAT [33]                                                                |

|                      |                                                                                                      |

|                      | tion measurement of TCAT memory cells showing a good performance years [33]                          |

|                      |                                                                                                      |

|                      | parison of the charge trap layer arrangement in (a) BiCS and (b) TCAT [35]70                         |

| •                    | ple structure of one memory cell of the vertical cylindrical floating-gate concept,                  |

|                      | nel induced by the overlapping control gate is illustrated, too [36]71                               |

| _                    | different approaches to fabricate a cylindrical floating-gate memory cell are                        |

|                      | cture comparable to the conventional floating-gate structure, middle) the                            |

|                      | control gate approach with improved CG-coupling and right) the Dual Control-                         |

|                      | ding Floating-gate structure with completely shielded CG and enhanced current                        |

|                      | ab]72                                                                                                |

|                      | parison of the coupling ratios for the conventional and extended sidewall control                    |

|                      | 72                                                                                                   |

| 9                    | sic structure of the ESCG 3D NAND array with 4 memory layers, b) cross                               |

|                      | he floating gate level showing the dimensions; c) electrical schematic of the                        |

|                      | [36]                                                                                                 |

|                      | ges applied for the needed operations: erase, program, inhibit of the neighboring                    |

|                      | milar to the conventional NAND schemes [36]                                                          |

| Figure 97. Equiv     | valent circuit of the DC-SF NAND cell string and voltages applied for the needed                     |

|                      | program and read [37]74                                                                              |

| Figure 98. a) Me     | asured ID-VG characteristic of DC-SF NAND device and b) TCAD simulation                              |

|                      | e cell architecture [37]74                                                                           |

| Figure 99. The ir    | nterference characteristics in between FG and FG (Vth difference of the adjacent                     |

| FG vs. Vth of the p  | programmed cell). Very small FG-FG coupling value of 12mV/V is obtained.                             |

|                      | 75                                                                                                   |

|                      | damental process steps to fabricate the memory array of the vertical cylindrical                     |

|                      | ture with Dual Control-gate and Surrounding Floating-gate [37]75                                     |

| 2 2                  | ArT NAND string [41]                                                                                 |

| Figure 102. Con      | nparison of the charge trap layer arrangement in (a) BiCS and (b) TCAT [35] and                      |

|                      | [ab]78                                                                                               |

| Figure 103. a) Widening of cell Vth distribution during cycling, compared for SMArT cell and                                                          |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 20nm planar FG-cell and b) Cell Vth distribution of high temperature retention after cycling of                                                       |     |

| SMArT Cell [41]                                                                                                                                       | 78  |

| Figure 104. Sectional view through the double channel structure of the VSAT concept, both                                                             |     |

| devices on the left and right side of the horizontal gate are driven simultaneously and they are                                                      |     |

| connected in series [21]                                                                                                                              |     |

| Figure 105. Overview on the final structure of a VSAT array including the PIPE fanout structure                                                       |     |

| [38]                                                                                                                                                  | 80  |

| Figure 106. Integration scheme to simplify the fanout of the horizontal gate lines with the PIPE structure [38]                                       |     |

| Figure 107. Comparison of the PIPE structure and the conventional structure using contacts with                                                       |     |

| different length to connect the stacked horizontal lines [38]                                                                                         | 81  |

| Figure 108. a) Cross sectional view along the string through the finally fabricated string, b)                                                        |     |

| detailed view at the memory stack and the poly-Si channel [38]                                                                                        |     |

| Figure 109. Schematic of one NAND string in the VSAT concept [38]                                                                                     | 82  |

| Figure 110. Transfer characteristic of either a single gate device or a double gate device                                                            |     |

| connected in series in the VSAT structure [38]                                                                                                        |     |

| Figure 111. Modifications to improve the performance of the deposited Si-channel by a) thinning                                                       |     |

| of the layer and b) forming gas anneal [38]                                                                                                           |     |

| Figure 112. a) Transfer characteristic during erase of VSAT memory device and b) extracted V <sub>T</sub> -                                           |     |

| shifts during program and erase of a single device with ±14V [38]                                                                                     | 84  |

| Figure 113. Limitation of the structural dimensions due to not ideally etch slopes through the                                                        |     |

| multilayer stacks, numbers of the assumption used for the feature size estimation for a) hole/trench formation and b) gate/channel formation [NaMLab] |     |

| Figure 116. Incremental step pulse programming slopes of three charge trap stacks (blue) and a                                                        | 00  |

| floating gate structure (yellow) [39]                                                                                                                 | 91  |

| Figure 117. Influence of the ISPP slope to the program disturb [NaMLab]                                                                               | 91  |

| Figure 118. Disturbance modes in a 3D Array (SMArT concept) [43]                                                                                      |     |

| Figure 119. Disturb bias conditions in a 3D Array (SMArT concept) [43]                                                                                |     |

| Figure 120. Comparison of the boost efficiency of different 3D concepts and main contributions                                                        |     |

| of the coupling [21]                                                                                                                                  | 93  |

| Figure 121. a) Channel boosting simulation for different WLs under inhibit condition for SMAr                                                         |     |

| concept and b) improved program disturbance fail bit by applying optimized conditions [41, 43]                                                        | 94  |

| Figure 122. Multi-bit per cell NAND Flash Memory Characteristics                                                                                      | 96  |

| Figure 123. Cell current and block size trend [41]                                                                                                    | 98  |

| Figure 124. Transfer characteristics of a charge trap memory cell during cycling of two devices                                                       |     |

| with different erase voltages [39]                                                                                                                    |     |

| Figure 125. Endurance and Power Consumption Comparison of V-NAND vs. Planar NAND [45]                                                                 |     |

| Figure 126. Development of the programmed distributions for a) charge trap and b) floating gate                                                       |     |

| memory array [39]                                                                                                                                     | 100 |

| Figure 127. Comparison of charge trap layer formation of a) BiCS and b) TCAT [35] and c)                                                              |     |

| SMArT [NaMLab]                                                                                                                                        | 100 |

| Figure 128. Two Options for Increasing Stacking Layers – 32 ➤ 64 layers                                                                               |     |

| Figure 129. Die size vs. Number for Device Layers for 256Gb Vertical Channel 3D NAND [51]                                                             |     |

| Figure 130. 3D NVM Evolution [49]                                                                                                                     |     |

| Figure 131. Intel/Micron 3D NAND [48]                                                                                                                 |     |

| Figure 132. Samsung V-NAND [45]                                                                                                                       |     |

| Figure 133. SanDisk NAND Roadmap [47]                                                                                                                 |     |

| Figure 134. SK Hynix 3D NAND Wafer                                                                                                                    | 113 |

| Figure 135. | NAND Flash Technology Roadmap [Forward Insights, NaMLab] | 114 |

|-------------|----------------------------------------------------------|-----|

| Figure 136. | NAND Flash Density Roadmap [Forward Insights, NaMLab]    | 115 |

| •           | 2D and 3D NAND Cost Trend [Forward Insights]             |     |

### **List of Tables**

| Table 1.  | Comparison of the characteristic electrical parameters of the different 3D concepts    | .18 |

|-----------|----------------------------------------------------------------------------------------|-----|

| Table 3.  | Number of Electrons per Logic Level [50]                                               | .95 |

| Table 4   | Specifications for NAND Flash vs. V-NAND [NAND datasheets, Forward Insights]           | .97 |

| Table 5.  | Comparison overview of the different concepts looking on all relevant aspects [Forward |     |

| Insights, | NaMLab]1                                                                               | 06  |

| Table 6.  | Comparison of 3D NAND Concepts by Company                                              | 13  |

#### Introduction

The NAND flash industry is at a technology inflection point. Planar floating gate NAND flash memory is facing fundamental scaling challenges with the upcoming 16nm node the last generation of planar technology. What's next?

Samsung's August 2013 announcement of the production of a 24-layer vertical string V-NAND shows the way forward. Vertical NAND or 3D NAND promises to continue increases in storage capacities and lower cost per bit necessary to enable emerging applications such as solid state drives and cold flash.

In the 2D planar era, the basic underlying floating gate technology (with a few exceptions) was essentially the same amongst all the NAND flash manufacturers. However in the 3D era, all NAND flash memory manufacturers are developing different 3D architectures.

**How 3D NAND Stacks Up** compares the 3D NAND alternatives and provides an independent view of the challenges, advantages and disadvantages of the various implementations and illuminates the 3D NAND status of the major industry players.

# XTEM along NAND string channel (Bitline Direction)

#### **Wordine Direction**

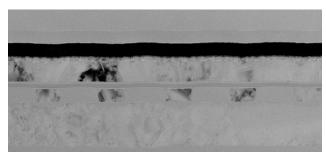

Figure 32. XTEMs dual gate SONOS devices [18]

The TEM cross section of Figure 32 illustrates the concept. It consists of a low thermal budget, inherently scalable, 3-D stackable, nitride based Flash solution with silicon TFT's having sub-50nm L and W devices built using standard CMOS fab tooling. Strings of up to 64 cells were fabricated with worst-case string currents in the 100's of nA's without special channel crystallization techniques and virtually zero read- and program-pass disturbs.

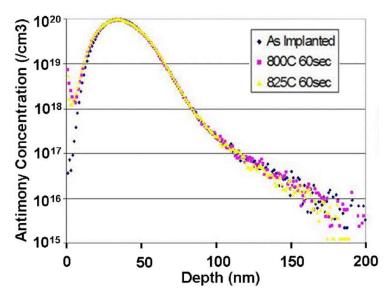

Figure 33. SIMS analysis of antimony-implanted LPCVD amorphous silicon, showing negligible diffusion [18]

Schiltron also addresses S/D formation. This is of even higher significance here since dopant diffusion in polycrystalline material is usually orders of magnitude greater than in monocrystalline silicon, a fact that would preclude the formation of ultra-short TFT's. In this research, however use is made of an extremely useful property of antimony where optimum activation in poly- and monocrystalline silicon occurs between 650°C and 800°C with no measurable diffusion. Figure 33 shows the SIMS analysis of antimony-implanted LPCVD amorphous silicon that subsequently underwent the illustrated thermal steps. This mimics the behaviour of the source and drain dopant

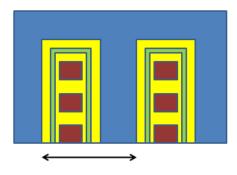

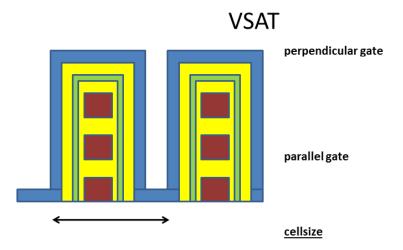

the following pages. The calculation leads to the smallest possible cell sizes and smallest feature size F which is required for the realization of the different 3D concepts.

## **VG-NAND**

parallel gate

perpendicular gate

cell size

Figure 114. Minimum dimensions for VG-NAND and VSAT [NaMLab]

#### **Performance**

The specifications for 19nm TLC and MLC NAND flash is contrasted with our estimates for MLC V-NAND in Table 4. The performance is primarily impacted by the array architecture, periphery circuitry and layout optimizations as well as the use of charge-trap technology.

| Specifications             | MLC 19nm | TLC 19nm | V-NAND MLC<br>3xnm 24-layer |

|----------------------------|----------|----------|-----------------------------|

| Density                    |          |          |                             |

| Page Size                  |          |          |                             |

| Block Size                 |          |          |                             |

| Voltage                    |          |          |                             |

| Operating I <sub>max</sub> |          |          |                             |

| Program Time               |          |          |                             |

| Block Erase (typ.)         |          |          |                             |

| Access Time t <sub>R</sub> |          |          |                             |

| Cycle Time                 |          |          |                             |

| Endurance (P/E cycles)     |          |          |                             |

| Retention                  |          |          |                             |

| ECC bits/ KB               |          |          |                             |

Table 4 Specifications for NAND Flash vs. V-NAND [NAND datasheets, Forward Insights]

| Most of the 3D concepts employ the charge trap stack for the memory element which benefits from |

|-------------------------------------------------------------------------------------------------|

|                                                                                                 |

|                                                                                                 |

| minimize the merge operation latency. For example, the block size of the 24-layer V-NAND is     |

| In addition                                                                                     |

| Concept<br>Criterion | 2D planar<br>NAND | NOR | VG-NAND | p-BiCS | stacked<br>cyl. FG | VSAT | TCAT /<br>SMArT |

|----------------------|-------------------|-----|---------|--------|--------------------|------|-----------------|

| Manufacturing        | IVAIID            |     |         |        | Cyl. 1 G           |      | SIVIALL         |

| complexity           |                   |     |         |        |                    |      |                 |

| Performance          |                   |     |         |        |                    |      |                 |

| Reliability          |                   |     |         |        |                    |      |                 |

| Disturb              |                   |     |         |        |                    |      |                 |

| Cost                 |                   |     |         |        |                    |      |                 |

| Cell size            |                   |     |         |        |                    |      |                 |

| Stackability         |                   |     |         |        |                    |      |                 |

| Scalability          |                   |     |         |        |                    |      |                 |

| MLC capability       |                   |     |         |        |                    |      |                 |

Table 5. Comparison overview of the different concepts looking on all relevant aspects [Forward Insights, NaMLab]

#### Comments:

| Manufacturing<br>Complexity | yield, defect density, manufacturability                           |  |  |

|-----------------------------|--------------------------------------------------------------------|--|--|

| Performance                 | PGM/ERS speed, read speed                                          |  |  |

| Reliability                 | endurance, retention                                               |  |  |

| Disturb                     | PGM disturb/read disturb immunity                                  |  |  |

| Cost (rel. cost/bit)        | die size, process complexity, manufacturability, yield             |  |  |

| Cell Size                   | physical cell size X/Y direction                                   |  |  |

| Stackability                | needed additional litho/process steps to stack an additional layer |  |  |

| Scalability                 | Ground rule scaling potential                                      |  |  |

| MLC capability              | is multi-bit storage really achievable                             |  |  |

2D planar 20nm NAND flash is a proven technology that has the smallest cell size and MLC capability but faces further scaling limitations. All 3D NAND concepts suffer from

Figure 137. 2D and 3D NAND Cost Trend [Forward Insights]

#### **About the Authors**

Florian Beug is Senior Technical Analyst for emerging memory technologies at Forward Insights. Florian's career spans 10 years in the field of non-volatile flash memory. He was memory cell engineer responsible for 48nm floating gate and 36nm floating gate NAND flash development and the pre-development of 2xnm floating gate and charge trapping NAND flash memory at Qimonda AG. In addition, Florian was a member of the NAND flash pre-development team at Infineon focusing on 75nm, 63nm and 32nm TwinFlash/NROM charge trapping technologies and also worked on embedded floating gate flash cells of Infineon Technologies, STMicroelectronics and Philips Semiconductors/NXP.

He is the author or co-author of more than 30 publications in the field of reliability, degradation characterization, and modeling of future NVM technologies and holds patents in this subject area.

Florian holds a Masters degree in solid state physics and a Ph.D in Electrical Engineering both from the University of Hannover, Germany.

**Thomas Melde** is at GlobalFoundries Dresden. Previously, he was a Scientist at NaMLab GmbH responsible for charge trap flash device characterization, simulation, and reliability modelling. Thomas' Ph.D. thesis focused on charge trap flash device development at the Flash pre-development team of Infineon/Qimonda, Dresden. He also worked as a research assistant at the Fraunhofer Institute, Division Design Automation, Dresden.

Thomas Melde received his diploma degree in electrical engineering at the Dresden University of Technology, Germany.

**Thomas Mikolajick** is Head of the Chair for Nanoelectronic Materials and Scientific Director at NaMLab GmbH. He is also Head of the German Society for Materials Science (DGM) working group "materials for non-volatile memories" and coordinator of the Cool Silicon Cluster <a href="http://www.cool-silicon.de/">http://www.cool-silicon.de/</a>. Previously, he was the Head of the Institute for Electronic- and Sensor Materials at TU Bergakademie Freiberg and lead new memory technologies and flash memory pre-development at Infineon Dresden.

Thomas holds 174 patents and received his Ph.D. in Electrical Engineering from the FAU Erlangen-Nuremberg, Germany.

**Stefan Slesazeck** is a Senior Scientist at NaMLab GmbH, responsible for concept evaluation, electrical characterization and modelling for various memories, such as resistive memory and ferroelectric field effect transistor. Prior to NaMLab, he was a project leader for the pre-development of new memory concepts with Qimonda Dresden (Germany) focusing on concept evaluation for 1T – DRAM including floating body devices, cell concepts, access schemes for WL-driver and sense amplifier. As a device engineer at Infineon Technologies, Stefan focused on the module development of 3D DRAM access devices in 65nm and 46nm buried word line technology and pre-development of 3D DRAM access devices for FinFET and EUD.

Stefan received a Ph.D. in microelectronics from the Dresden University of Technology, Germany.

Gregory Wong is the Founder and Principal Analyst of Forward Insights. Greg has in-depth knowledge of the cost, performance and markets and applications of multi-bit per cell NOR, NROM and NAND flash memories, emerging memories and solid state drives. Greg previously held a number of management positions in strategic planning, business development and engineering at Hitachi, Siemens, ProMOS and Qimonda/Infineon. At Infineon/Qimonda, Greg was responsible competitive intelligence and reverse engineering for flash memories focusing on flash memory vendors' strategies, process technologies, design architectures, product performance, manufacturing capabilities and costs.

Greg earned his B.A.Sc. degree in Electrical Engineering from the University of Toronto, and his M.B.A. degree from the Richard Ivey School of Business in London, Ontario.

#### **About NamLab**

#### NaMLab (Nano-electronic Materials Laboratory)

The research at NaMLab focuses on materials for electronic devices and new device concepts. Among these are high-k materials for capacitors, transistors and other applications, novel switching devices including memristors, nanowire based electronics as well as materials for energy harvesting devices such as solar cells.

Future nano-electronic products require the development of new materials that are not currently available. NaMLab consequently focuses its research activities on materials and applications that show the potential to offer significant advantages over materials and products used today. In addition to investigating and characterizing new materials, NaMLab is undertaking research on the integration of these materials into semiconductor products with nano-scale dimensions.

NaMLab, originally founded as a research joint venture between Qimonda AG and the TU Dresden in July 2006, has its roots in the Corporate Research Department of Infineon AG and is now owned completely by the Technical University of Dresden. NaMLab receives basic financing from the Saxon Ministry of Science and Arts (SMWK). The company benefits from excellent working conditions in its office and clean room building opened in October 2007 and located within the TU Dresden campus.

#### Characterization:

- physical characterization (conductive AFM, SSRM, SEM)

- electrical device characterization;

- 200mm/300mm wafer probe stations

- 5K 500K temperature range

- Analytical measurements of memory cells (lifetime, switch time, storage and deletion windows, endurance and retention)

- charge carrier mobility with Hall and split-C(U)

- optical characterization (FTIR ellipsometry, µRaman and photoluminescence)

- dielectric reliability (TDDB, BTI, SILC, TDDS, TSCIS)

- high-k material development

- oxides: AlO, TiO, ZrO, HfO and mixtures

- metals: Al, Pt, Au, TiN, Ti, Ru

- methods: ALD, MBE, PVD, evaporation

#### Development:

- materials for emerging memories

- high-k stacks for capacitors and transistors

- development of new memory concepts

- charge trap device development

- development of explorative devices based on silicon nano wires

#### **Contact**

NaMLab gGmbH Noethnitzer Str. 64 01187 Dresden Germany T +49.351.21.24.990-00 F +49.351.475.83.900

E-mail: info@namlab com

www.namlab.com

#### **About Forward Insights**

Forward Insights provides independent, insightful market research, consulting and information services focusing on semiconductor memories and solid state storage. The company offers unparalleled depth and understanding of the strategic, market and technical complexities of the semiconductor memory landscape.

#### **Services**

Forward Insights offers a unique and comprehensive strategic, financial, market and technical perspective on the semiconductor memory industry. The professional services offered include:

- Strategy Consulting

- Financial & Cost Analysis

- Market Forecasts

- Technology Analysis

- Competitive Analysis

- Surveys

- Training

- Custom projects

#### Contact

12 Appian Dr.

North York, Ontario

Canada M2J 2P6

Tel.: +1-408-565-8207

E-mail: <a href="mailto:greg@forward-insights.com">greg@forward-insights.com</a>

Market and technical intelligence for semiconductor memories, emerging memory technologies and solid state drives.

www.forward-insights.com